Introduction

Logic gates serve as the building blocks to digital logic circuits

using combinational logic. We're going to consider the following

gates: NOT gates (also called inverters), AND gates, OR gates,

NAND gates, NOR gates, XOR gates, and XNOR gates.

We'll also discuss the concept of gate deltay.

NOT gates

NOT gates or

inverters have a single bit input and a single

bit of output.

This is a diagram of a NOT gate. It is a triangle with a circle

on the right. The circle indicates "negation".

The truth table defines the behavior of this gate.

where

x is the input and

z is the output.

AND2 gates

AND

2 gates have two bits of input and a single bit of

output. The subscript, 2, indicates how many inputs this AND gate

has. For example, AND

3 gates have 3 inputs.

The output of AND

2 gate is 1 only if both inputs

are 1. Otherwise, the output is 0.

The truth table defines the behavior of this gate.

| x1 |

x0 |

z |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

1 |

The function implmented by

AND2 gates has interesting

properties:

- The function is symmetric. Thus, x * y == y * x.

This can be verified by using truth tables. We use * to

represent AND2.

- The function is associative. Thus, (x * y) * z ==

x * (y * z). This can be verified by using truth tables.

Because of these properties, it's easy to define

ANDn,

which is an n-input

AND gate.

ANDn(x1, x2,...,xn)

= x1 * x2 * ... * xn

That is, an AND gate with n-inputs is the AND of all the bits.

This is not ambiguous because the AND function is associative (all

parenthesization of this expression are equivalent).

OR2 gates

OR

2 gates have two bits of input and a single bit of

output. The subscript, 2, indicates how many inputs this OR gate

has. For example, OR

3 gates have 3 inputs.

The output of OR

2 gate is 0 only if both inputs

are 0. Otherwise, the output is 1.

The truth table defines the behavior of this gate.

| x1 |

x0 |

z |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

The function implemented by

OR2 gates has interesting

properties:

- The function is symmetric. Thus, x + y == y + x.

This can be verified by using truth tables. We use "+" to

represent OR2

- The function is associative. Thus, (x + y) + z ==

x + (y + z). This can be verified by using truth tables.

Because of these properties, it's easy to define

ORn,

which is an n-input

OR gate.

ORn(x1, x2,...,xn)

= x1 + x2 + ... + xn

That is, an AND gate with n-inputs is the AND of all the bits.

This is not ambiguous because the AND function is associative (all

parenthesization of this expression are equivalent).

NAND2 gates

NAND

2 gates have two bits of input and a single bit of

output. The subscript, 2, indicates how many inputs this NAND gate

has. For example, NAND

3 gates have 3 inputs.

NAND

k gates is define unusually. Since NAND

2

is

not associative, the definition is based on AND

2.

In particular

NANDk(x1, x2,...,xn)

= NOT( ANDk(x1, x2,...,xn) )

Thus, NAND

k is the negation of AND

k.

The truth table defines the behavior of this gate. It's the

negation of

AND2.

| x1 |

x0 |

z |

| 0 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

The function implemented by

NAND2 gates has interesting

properties:

- The function is symmetric. Thus, x NAND y == y NAND x.

This can be verified by using truth tables.

- The function is not associative. This can be verified

by using truth tables.

Because of these properties,

NANDk is defined

from

ANDk, and

not built from

NAND2 gates.

NOR2 gates

OR

2 gates have two bits of input and a single bit of

output. The subscript, 2, indicates how many inputs this OR gate

has. For example, NOR

3 gates have 3 inputs.

The output of NOR

2 gate is the negation of

OR

2.

The truth table defines the behavior of this gate.

| x1 |

x0 |

z |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

0 |

The function implmented by

NOR2 gates has interesting

properties:

- The function is symmetric. Thus, x NOR y == y NOR x.

This can be verified by using truth tables.

- The function is not associative. This can be verified

by using truth tables.

Because of these properties,

NORk is defined from

ORk, and

not built from

NOR2 gates.

XOR2 gates

XOR

2 gates have two bits of input and a single bit of

output.

The output of XOR

2 gate is 1 only if the inputs

have opposite values. That is, when one input has value 0, and

the other has value 1.. Otherwise, the output is 0.

This is called

exclusive-or. The definition of

OR

2 is

inclusive-or, where the output is

1 if either input is 1, or if both inputs are 1.

XOR

2 can be defined using AND

2, OR

2,

and NOT.

x XOR y == ( x AND (NOT y) ) OR ( (NOT x) AND y )

== x\y + y\x

Here's a diagram of the XOR

2 gate.

If you look carefully at the drawing of the gate, there is a second

arc behind the first one near the inputs. Since this second arc

is hard to see, it's usually a good idea to write the word "XOR" inside

the gate.

The truth table defines the behavior of this gate.

| x1 |

x0 |

z |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

The function implmented by

XOR2 gates has interesting

properties:

- The function is symmetric. Thus, x (+) y == y (+) x.

This can be verified by using truth tables. (We use (+) to denote

logical XOR--ideally, we'd draw it with a + sign inside a circle,

but HTML doesn't seem to have a symbol for this).

- The function is associative. Thus, [ x (+) y ] (+) z ==

x (+) [ y (+) z ]. This can be verified by using truth tables.

Because of these properties, it's easy to define

XORn,

which is an n-input

XOR gate.

XORn(x1, x2,...,xn)

= x1 (+) x2 (+) ... (+) xn

That is, an XOR gate with n-inputs is the XOR of all the bits.

This is not ambiguous because the XOR function is associative (all

parenthesization of this expression are equivalent).

XNOR2 gates

XNOR

2 gates have two bits of input and a single bit of

output.

The output of XNOR

2 gate is the negation of

XOR

2 and has 1 when both inputs are the same.

If you look carefully at the drawing of the gate, there is a second

arc behind the first one near the inputs. Since this second arc

is hard to see, it's usually a good idea to write the word "XNOR" inside

the gate.

The truth table defines the behavior of this gate.

| x1 |

x0 |

z |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

The function implmented by

XNOR2 gates has interesting

properties:

- The function is symmetric. Thus, x XNOR y == y XNOR x.

This can be verified by using truth tables.

- The function is associative. Thus, (x XNOR y) XNOR z ==

x XNOR (y XNOR z). This can be verified by using truth tables.

Because of these properties, it's easy to define

XNORn,

which is an n-input

XNOR gate.

XNORn(x1, x2,...,xn)

= x1 XNOR x2 XNOR ... XNOR xn

That is, an XNOR gate with n-inputs is the XNOR of all the bits.

This is not ambiguous because the XNOR function is associative (all

parenthesization of this expression are equivalent).

(Error-checkers! You may wish to verify this, and email

me if this is incorrect!).

Building Blocks

We can use logic gates to build circuits. While we've described 6

gates, you can do with only three gates to build all possible

circuits:

AND2,

OR2, and

NOT. In fact, you don't even need all three gates. It can be

done in two kinds of gates of less. We'll explain in a future

section.

These circuits can implement any truth table.

Valid Combinational Circuits

The inverse is not true. Not every circuit that is built from

gates corresponds to a truth table. In particular, you must observe

the following rules if it's to correspond to a truth table.

- The output of a gate may only be attached to the input

of another gate. (Think of this as a directed edge from output to

input).

- There must be no cycles in the circuit. Treat the circuit

like a directed graph with directed edges defined in the previous

item.

- Although the output of a gate may be attached to more than

one input, an input may not have two different outputs attached to

it (this would create conflicting input signals).

- Each input of a gate must come from either the output of

another gate or a source. A source is a source that generates

either a 0 or 1.

Gate Delay

Real gates have delay. In other words, if you change the

value of the inputs, say from 0 and 0 to 0 and 1, then the output

takes some small amount of time before it changes. This delay

is called

gate delay.

This delay is due to the fact that information can travel

at most, the speed of light, and in reality, the time it takes

to do the computation is not infinitely quick.

This delay limits how fast the inputs can change and yet the

output have meaningful values. It also allows certain kinds

of circuits to be created that don't follow the rules from

the previous section. In particular, flip flops (to be discussed

later) can be generated from gates that use cycles.

Why Subscripts?

Most books don't distinguish between an

AND2

gate and a

AND3 gate. They claim an AND gate

is an AND gate, regardless of the number of inputs.

While this is true, I subscript it because an

AND2

and an

AND3 do not have the same truth table. In

particular, an

AND2 truth table has 4 rows while

an

AND3 has 8. While the two truth tables are

related, they still define different functions.

Thus, I make the distinction by subscripting the number of inputs.

Summary

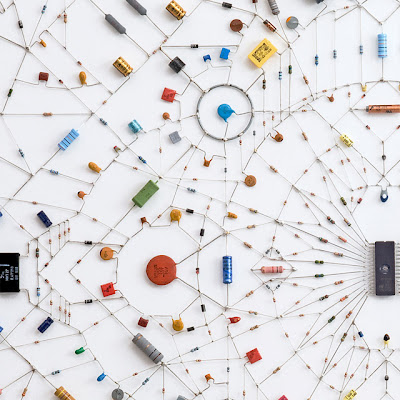

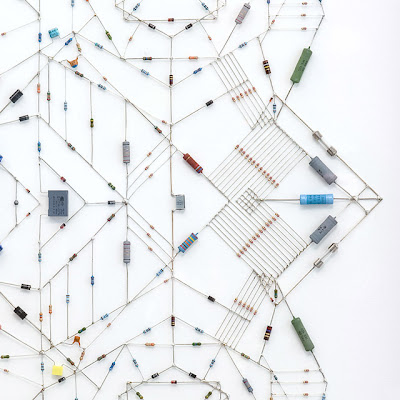

Logic gates are the building blocks of combinational logic

circuits. You can buy logic gates from electronic hobby places.

These gates are primarily for hobbyists. Each chip usually has

about 4 logic gates.

Real computers don't use these kinds of gates, because they take

far too much space. With VLSI technology, you can cram millions of

gates onto a wafer no bigger that your thumbnail.

The behavior of logic gates can be described by truth tables.

However, because these gates are "physical", they have some properties

not expressed in truth tables. In particular, gate delay describes

the amount of time it takes for the output to change when the input

changes. This time is not zero, thus, one must wait a short amount

of time for the output to take effect.

We'll discuss how to build circuits from these gates in

a later set of notes.